Matière

- Matière et Energie

- Electronique

Edito : Que sera l’électronique de l’après silicium ?

- Tweeter

-

-

10 avis :

C’est peu de dire que l’invention du transistor en 1947 puis, dans son prolongement, celle du microprocesseur en 1971 compte parmi les ruptures technologiques les plus importantes de l’histoire de l’humanité. En effet, sans transistors et sans puces électroniques, l’informatique, les télécommunications et le multimédia n’auraient jamais connu la fulgurante évolution à laquelle nous avons assisté depuis un demi-siècle et l’Internet, moteur de la rupture de société la plus importante depuis l’invention de l’imprimerie, serait encore dans les limbes.

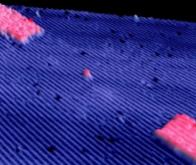

Depuis la commercialisation du premier microprocesseur, il y a moins de 50 ans, le chemin parcouru a été vertigineux : alors que la première puce d’Intel comptait un peu plus de 2000 transistors, nous savons aujourd’hui en intégrer 10 milliards dans un microprocesseur et IBM a annoncé un nouveau procédé de gravure qui va permettre de concevoir une puce de la taille d'un ongle, pouvant contenir 30 milliards de transistors ! Cette technologie met en œuvre une finesse de gravure de seulement 5 nm grâce à des dépôts de nanoparticules de silicium et l'utilisation d'ultraviolets extrêmes (EUV). Si la technologie EUV n'est pas nouvelle, le dépôt de nanoparticules de silicium constitue une rupture face à la technologie FinFET (Fin Field-Effect Transistor) utilisée actuellement pour la gravure, mais qui aura du mal à descendre en dessous des 7 nm.

Selon IBM, les puces à 5 nm offrent un gain de performances de 40 % par rapport aux circuits 10 nm actuels, ou une économie d'énergie de 75 % pour le même niveau de performances. Il faut en effet rappeler que lorsque la densité augmente, la transmission du signal entre les transistors devient plus rapide. C’est en gagnant sur ces deux tableaux qu’il est possible de construire des ordinateurs portables, des tablettes et des smartphones toujours plus rapides et de moins en moins gourmands en énergie.

Pour arriver à ce record, IBM s'est associé à Samsung et GlobalFoundries. Il y a deux ans, les partenaires ont annoncés une finesse de gravure à 7 nm permettant de mettre 20 milliards de transistors sur une puce. Cette technologie sera utilisée dans quelques semaines dans l'usine Fab 8 de GlobalFoundries aux Etats-Unis. En revanche, les puces gravées en 5 nm ne sont pas attendues avant 2020.

Ces nouvelles puces seront également au cœur de l’intelligence artificielle et des composants qui vont favoriser l’explosion du Web 3.0, c’est-à-dire l’internet des objets. Ce nouveau réseau d’intelligence planétaire connectée relie déjà plus de 12 milliards d’objets mais, selon les dernières prévisions de l’Idate, il en reliera le triple dans 10 ans et pourrait générer 1 500 milliards de dollars d’activités dans l’économie mondiale à l’horizon 2030. IBM, comme tous les géants de l’électronique et du numérique, ne s’y est pas trompé et, comme le souligne Arvind Krishna, directeur de IBM Research, « L'avancement de la technologie des semi-conducteurs est essentiel pour que les entreprises puissent répondre aux demandes de l'informatique cognitive dans les années à venir ».

Avec cette perspective prochaine de 30 milliards de transistors sur une seule puce, IBM fait mentir certaines prévisions pessimistes et montre que les limites de la loi de Moore, établie en 1965 et prévoyant un doublement tous les 18 mois, puis tous les deux ans, du nombre de transistors implantés sur un microprocesseur, ne sont pas encore atteintes. Certes, le passage de 20 à 30 milliards de transistors ne correspond pas à une multiplication par deux, mais que de chemin parcouru depuis le premier microprocesseur d'Intel, le 4004, qui intégrait, je le rappelle, en 1971 seulement... 2300 transistors !

Il y a quelques semaines, le fondeur taiwanais TSMC annonçait pour sa part qu’il commençait la production de puces gravées en 7 nm, parmi lesquelles on trouve la future puce Apple A12. Reste que le passage sous les 22 nm a demandé l’abandon des transistors planaires, au profit de « transistors 3D » comme les FinFET. Le passage sous les 7 nm passera sans doute par l’utilisation de nouveaux transistors FinFET ou des transistors GAA, voire l’abandon du silicium. TSMC, comme IBM, prévoit une finesse de gravure de 5 nm vers 2020. C’est Apple qui devrait en bénéficier avec ses futures puces A14 qui équiperont sa prochaine génération de smartphone et permettront une puissance accrue de 45 % et une consommation réduite de 20 %.

Samsung, le géant coréen de l’électronique, est également bien décidé à rester dans cette cours effrénée à la miniaturisation extrême. Il travaille déjà sur la génération de puces en 3 nanomètres, considérée comme proche des limites de la loi de Moore. Dans ces futurs microprocesseurs, chaque transistor fera de 10 à 15 atomes de largeur et sera 30 000 fois plus fin qu'un cheveu. Pour parvenir à produire ces puces, Samsung envisage de construire une usine qui coûtera au moins 20 milliards de dollars, dix fois plus chère que les usines actuelles…

Pour réussir ce nouveau bond en avant, Samsung Electronics va abandonner la technologie de lithographie à rayons d'une longueur d'onde de 193 nanomètres, pour passer à une lithographie aux UV extrêmes à 10 nanomètres. Cette future génération de puces gravées en 3 nanomètres mettra en œuvre une nouvelle technologie de transistor à nanofeuille, baptisée GAA. Ce changement de structure de transistor s’impose pour contenir l’augmentation des courants de fuites, un phénomène physique qui apparaît lorsqu’on se rapproche du niveau atomique.

Quant à Intel, il ne prévoit pas le passage à la gravure en 10 nm avant 2019 mais affirme que ces nouvelles puces gravées en 14 nm, Whiskey Lake et Amber Lake, seront deux fois plus puissantes que celles qui équipaient un portable il y a cinq ans et permettront d’atteindre une autonomie record de 16 heures de travail. Les prochaines puces d’Intel, gravées en 10 nm, vont multiplier par 2,7 la densité en transistors par rapport aux puces actuelles gravées en 14 nm. Intel pourrait y intégrer environ 100 millions de transistors par mm², soit quelque 12 milliards de transistors par processeur de nouvelle génération, pour une puissance de calcul de plus de 10 000 milliards d'opérations par seconde !

Que de chemin parcouru depuis 1951, quand un transistor faisait encore un centimètre de large. En 1971, le premier microprocesseur d’Intel intégrait quelques milliers de transistors d’une taille de 10 microns, soit le centième d’un millimètre. On dénombre désormais 1 milliards de transistors sur un seul microprocesseur et la puissance informatique a été multipliée par cent millions de milliards.

Notons que cette course sans fin à la miniaturisation a été facilitée par le procédé FD-SOI (Fully Depleted Silicon on Insulator), mis au point par la société iséroise Soitec (issue du CEA-LETI) avec le concours de STMicroelectronics. Le FD-SOI a pour objectif de réduire, voire d’annuler les courants de fuite parasites, dont l’importance grandit à mesure que la miniaturisation des transistors progresse. Cette nouvelle technologie consiste à superposer, sur le matériau brut en silicium, une couche d’oxyde amorphe de 20 nm d’épaisseur puis une autre couche de silicium de 6 nm d’épaisseur, où sont implémentés les canaux du transistor. La couche d’oxyde agit comme un isolant et confine les électrons entre la source et le drain.

Les premiers produits bénéficiant de circuits FD-SOI sont sur le marché depuis 2016. C’est par exemple le cas de la « Smartwatch » de Sony, dont le circuit GPS réalisé à partir d’un substrat FD-SOI consomme cinq fois moins d’énergie et permet une autonomie de 35 heures. Mais en dépit des progrès incessants, la fin de la loi de Moore se profile inexorablement à l’horizon. C’est en tout cas ce que confirme le livre blanc « More Moore » publié récemment par le groupe de travail IRDS de la société savante IEEE sous la direction de Paolo Gardini, ancien directeur de la technologie chez Intel (Voir IEEE).

Selon cette étude prospective, il resterait cinq générations, pour passer de 7 nanomètres en 2019 à 2 nanomètres en 2030, un seuil considéré comme ultime avec les technologies actuelles, compte tenu des lois de la physique. L’étude souligne toutefois qu’à partir de la génération de 5 nanomètres prévue en 2021, il faudra utiliser d’autres technologies et avoir recours à de nouveaux matériaux et modes de gravure pour pouvoir continuer de respecter la loi de Moore. Concrètement, cela veut dire que les composants élémentaires ne seront pas plus petits mais que les puces auront néanmoins globalement des performances accrues.

Reste qu’à l’horizon 2030, avec des transistors qui mesureront moins de deux nanomètres (environ 15 atomes de silicium), on se rapprochera du mur infranchissable de Moore, à moins qu’une ou plusieurs révolutions technologiques permettent de dépasser cette limite fatidique, pour pouvoir poursuivre cette triple course inlassable : toujours plus petit, toujours plus puissant, toujours moins cher.

De nombreuses équipes de recherche dans le monde préparent déjà cette transition technologique. Fin 2016, des chercheurs du Laboratoire national Lawrence-Berkeley (université de Californie) ont ainsi créé un transistor avec une grille fonctionnelle mesurant à peine 1 nanomètre de long. À titre de comparaison, ils précisent qu'un cheveu humain mesure en moyenne 50 000 nanomètres d'épaisseur. La grille agit comme un interrupteur et détermine si le transistor est ouvert ou fermé. Elle contrôle ainsi le passage du courant. Mais en deçà d'une certaine taille (de l’ordre de 5 nm), ce contrôle par la grille du flux d'électrons est altéré par le fameux « effet tunnel » prévu par la physique quantique. Mais ces chercheurs américains ont réussi à surmonter cet obstacle majeur en utilisant des nanotubes de carbone pour la grille et du disulfure de molybdène (MoS2) à la place du silicium.

Au début de cette année, des chercheurs de l’Unité mixte de physique CNRS/Thales, en collaboration avec l’université de Cambridge, sont parvenus, quant à eux, en combinant la lithographie ultraviolette, l’irradiation ionique et le transfert de graphène par vaporisation chimique sur un substrat de supraconducteur à haute température, à fabriquer une jonction entre un supraconducteur à haute température et du graphène et à rendre le graphène supraconducteur par effet de proximité (Voir Nature). Ils ont également montré qu’en modifiant le dopage du graphène par application d’une différence de potentiel, on peut créer une modulation de la barrière au niveau de la jonction, permettant ainsi de contrôler son état fermé ou ouvert. Ces travaux ouvrent la voie à la fabrication industrielle de véritables transistors supraconducteurs, à commutation hyper-rapide pour le traitement de l’information.

La voie de l’ordinateur optique pourrait également, de manière complémentaire à l’électronique sur silicium et à l’informatique quantique, déboucher sur des systèmes de calcul beaucoup plus puissants que les meilleures machines actuelles. La jeune société LigthOn, basée à Paris, a ainsi fait sensation il y a peu en présentant un accélérateur optique de calcul. Ce système remplace les électrons par les photons et utilise les particularités physiques de ces particules élémentaires de lumière pour réaliser des calculs hyperrapides par multiplication de matrices. Et le résultat est pour le moins impressionnant puisqu’une récente démonstration a permis de vérifier que l’accélérateur optique de LightOn permettait de multiplier par 800 la vitesse de calcul par rapport à une puce classique dotée de 64 Go de RAM, de quoi permettre à court terme la diffusion et l’accès au supercalcul à l’ensemble de l’économie, de l’industrie et de la recherche…

En 2016, une autre équipe du Leti a pour sa part réussi à produire le premier qbit silicium construit selon les procédés de la technologie CMOS (Complementary Metal Oxyde Semiconductor), le standard de fabrication de la microélectronique classique. On conçoit sans peine les avantages d'un tel choix, qui réunit en quelque sorte le meilleur des deux mondes, informatique classique et informatique quantique, et les rend mutuellement compatibles. Comme le précise Maud Vinet, chargée de ce programme au CEA, « La technologie du silicium a atteint un tel niveau de maîtrise en nanomètres que notre technologie nous permettrait théoriquement de mettre 10 milliards de qbits sur un centimètre carré de silicium.

Cette perspective d’une puce quantique sur silicium, encore impensable il y a cinq ans, devient d’autant plus plausible que le CEA et le Leti ont récemment réussi à mettre au point des plaques de silicium dont la couche supérieure ne contient que 0,006 % de silicium 29, soit environ 800 fois moins que le silicium actuel qui présente le gros défaut, à cause de la forte présence de ce silicium 29, de perturber le spin des électrons et de détruire très rapidement les qbits nécessaires au calcul quantique.

Début juillet, le géant américain Microsoft a présenté l'avancement de ses recherches en matière d'informatique quantique et a créé la surprise en annonçant qu’il commercialiserait son premier ordinateur quantique opérationnel d’ici 2023. De manière très intéressante, l’approche technologique de Microsoft se démarque de celles de ses grands concurrents et se focalise sur la création de qbits topologiques, beaucoup moins sensibles à la décohérence, c’est-à-dire la perte de leur capacité de calcul.

Pour produire des qbits topologiques stables, Microsoft utilise des fermions (les fermions constituent la famille de particules qui forment la matière) de Majorana, une étrange particule qui est sa propre antiparticule et qui a été prévue en 1937 par le génial physicien italien Ettore Majorana, mystérieusement disparu en 1938. L'existence de cette particule a été prouvée en 2012 par l'Université de Delft aux Pays-Bas, et Microsoft serait parvenu à les contrôler pour en faire des qbits topologiques, d’une précision 1000 fois supérieure à celle des qbits conventionnels.

L’arrivée possible d’un premier ordinateur quantique stable et opérationnel américain ou européen d’ici cinq ans permettrait non seulement de pulvériser la loi de Moore mais changerait également complètement la donne en matière de supercalcul. Selon le classement du Top 500 des supercalculateurs les plus performants au monde, il y avait, fin 2017, 202 machines chinoises et 143 calculateurs américains, tandis que l’Europe ne dispose que de 84 superordinateurs, et le Japon, 35. Actuellement, c’est le Summit américain qui est devenu depuis juin dernier l'ordinateur le plus puissant du monde avec ses 122 petaflops (122 millions de milliards d'opérations par seconde) contre 93 petaflops pour le Sunway TaihuLight chinois, qui a perdu la place de leader. Dans cette compétition mondiale pour la maîtrise de l’hyperpuissance informatique, indispensable au développement de l’économie numérique, les Etats-Unis et la Chine dominent clairement tous les autres pays et ensembles politiques, y compris l’Europe.

Heureusement, la Commission européenne vient d’annoncer, il y a quelques semaines, un ambitieux projet (doté d’un budget total de 2,7 milliards d’euros), le « High Performance Computing » (EuroHPC), qui consiste à mutualiser les moyens des États membres pour construire et partager des superordinateurs hexaflopiques - c’est-à-dire capable d’effectuer plus d’un milliard de milliard d’opérations par seconde - d’ici 2023. Dans cette compétition hautement stratégique, la France se tient en bonne place : elle occupe depuis juin dernier, au Top 15 des superordinateurs, la 14eme place mondiale et la première place européenne, grâce à son Tera1000, une machine de 25 petaflops de puissance.

Si personne ne peut dire aujourd’hui ce que seront l’électronique et l’informatique dans dix ans, ce qui est certain c’est que la combinaison des différents pistes technologiques que j’ai évoquées – puce supraconductrice, puce optique, puce quantique – devrait permettre de franchir à l’horizon 2030 cette fameuse loi de Moore pour entrer dans l’ère de l’hypercalcul partagé. Fonctionnant en réseau et démultipliant leurs ressources et leur puissance, ces futurs systèmes informatiques auront des vitesses de calcul absolument vertigineuses qui seront de 1000 à un million de fois supérieures à celles des plus grosses machines actuelles !

Il en résultera un saut non pas quantitatif mais qualitatif vers une économie de la conception et de la production en temps réel, entièrement personnalisée, de biens et de services, non seulement en matière de consommation, d’habitat et de transport mais également dans le domaine de la santé, où il deviendra possible de concevoir et de produire en quelques heures une molécule sur mesure exactement adaptée à la pathologie d’une personne donnée, ou encore dans le secteur des loisirs, où l’on pourra proposer à chacun des espaces virtuels de distraction d’une richesse infinie, intégrant tous ses éléments affectifs et ses préférences culturelles et esthétiques... Mais la grande question qui agite et divise la communauté scientifique est de savoir si l’arrivée annoncée de cette puissance de calcul presque inimaginable d’ici 10 ou 15 ans peut permettre l’émergence d’une forme d’intelligence artificielle autonome, consciente d’elle-même et agissant selon ses propres finalités…

Face à ces mutations de société qui sont pour demain, il est plus que jamais urgent que nous réfléchissions ensemble sur le cadre et les finalités politiques sociales, culturelles et éthiques que nous voulons donner à ce nouveau et prodigieux chapitre de l’histoire humaine.

René TRÉGOUËT

Sénateur honoraire

Fondateur du Groupe de Prospective du Sénat

Noter cet article :

Vous serez certainement intéressé par ces articles :

L’électronique pétahertz repousse les limites du traitement de l’information

L’électronique à ondes lumineuses est en passe de bouleverser les technologies de l'information. Cette approche novatrice intègre les systèmes optiques et électroniques à des vitesses vertigineuses, ...

Des chercheurs américains identifient un matériau qui conduit mieux l’électricité dans les puces électroniques

Des chercheurs de Stanford Engineering ont mis au point un matériau ultrafin qui conduit l’électricité mieux que le cuivre et qui pourrait permettre à la nanoélectronique d’être plus économe en ...

L'électronique comestible biodégradable au service de la médecine

Alors que nous ingérons par inadvertance environ 1 milligramme de phtalocyanine de cuivre à chaque fois que nous nous brossons les dents, ces cristaux pourraient être exploités comme des transistors ...

Recommander cet article :

- Nombre de consultations : 434

- Publié dans : Electronique

- Partager :